ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

134

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

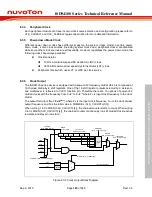

Application Interrupt and Reset Control Register (AIRCR)

Register

Offset

R/W Description

Reset Value

AIRCR

0xD0C

R/W Application Interrupt and Reset Control Register

0xFA05_0000

31

30

29

28

27

26

25

24

VECTORKEY

23

22

21

20

19

18

17

16

VECTORKEY

15

14

13

12

11

10

9

8

ENDIANNESS

Reserved

PRIGROUP

7

6

5

4

3

2

1

0

Reserved

SYSRESETRE

Q

VECTCLRAC

TIVE

VECTRESET

Bits

Description

[31:16]

VECTORKEY

Register Access Key

When writing this register, this field should be 0x05FA, otherwise the write action will be

unpredictable.

The VECTORKEY filed is used to prevent accidental write to this register from resetting the

system or clearing of the exception status.

[15]

ENDIANNESS

Data Endianness

0 = Little-endian.

1 = Big-endian.

[14:11]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[10:8]

PRIGROUP

Interrupt Priority Grouping

This field determines the Split Of Group priority from subpriority,

[7:3]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[2]

SYSRESETREQ

System Reset Request

Writing This Bit to 1 Will Cause A Reset Signal To Be Asserted To The Chip And Indicate A

Reset Is Requested

This bit is write only and self-cleared as part of the reset sequence.

[1]

VECTCLRACTIVE

Exception Active Status Clear Bit

Setting This Bit To 1 Will Clears All Active State Information For Fixed And Configurable

Exceptions

This bit is write only and can only be written when the core is halted.

Note:

It is the debugger’s responsibility to re-initialize the stack.

[0]

VECTRESET

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.