ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

717

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

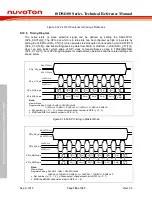

SPI FIFO Control Register (SPI0_FIFOCTL)

Register

Offset

R/W Description

Reset Value

SPI0_FIFOCTL

0x10

R/W SPI0 FIFO Control Register

0x4400_0000

31

30

29

28

27

26

25

24

Reserved

TXTH

Reserved

RXTH

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

TXFBCLR

RXFBCLR

7

6

5

4

3

2

1

0

TXUFIEN

TXUFPOL

RXOVIEN

RXTOIEN

TXTHIEN

RXTHIEN

TXRST

RXRST

Bits

Description

[31]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write

with reset value.

[30:28]

TXTH

Transmit FIFO Threshold

If the valid data count of the transmit FIFO buffer is less than or equal to the TXTH

setting, the TXTHIF bit will be set to 1, else the TXTHIF bit will be cleared to 0.

[27]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write

with reset value.

[26:24]

RXTH

Receive FIFO Threshold

If the valid data count of the receive FIFO buffer is larger than the RXTH setting, the

RXTHIF bit will be set to 1, else the RXTHIF bit will be cleared to 0.

[23:10]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write

with reset value.

[9]

TXFBCLR

Transmit FIFO Buffer Clear

0 = No effect.

1 = Clear transmit FIFO pointer. The TXFULL bit will be cleared to 0 and the TXEMPTY

bit will be set to 1. This bit will be cleared to 0 by hardware about 1 system clock after

it is set to 1.

Note:

The TX shift register will not be cleared.

[8]

RXFBCLR

Receive FIFO Buffer Clear

0 = No effect.

1 = Clear receive FIFO pointer. The RXFULL bit will be cleared to 0 and the RXEMPTY

bit will be set to 1. This bit will be cleared to 0 by hardware about 1 system clock after

it is set to 1.

Note:

The RX shift register will not be cleared.

[7]

TXUFIEN

TX Underflow Interrupt Enable Bit

When TX underflow event occurs in Slave mode, TXUFIF (SPI0_STATUS[19]) will be

set to 1. This bit is used to enable the TX underflow interrupt.

0 = Slave TX underflow interrupt Disabled.