ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

912

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

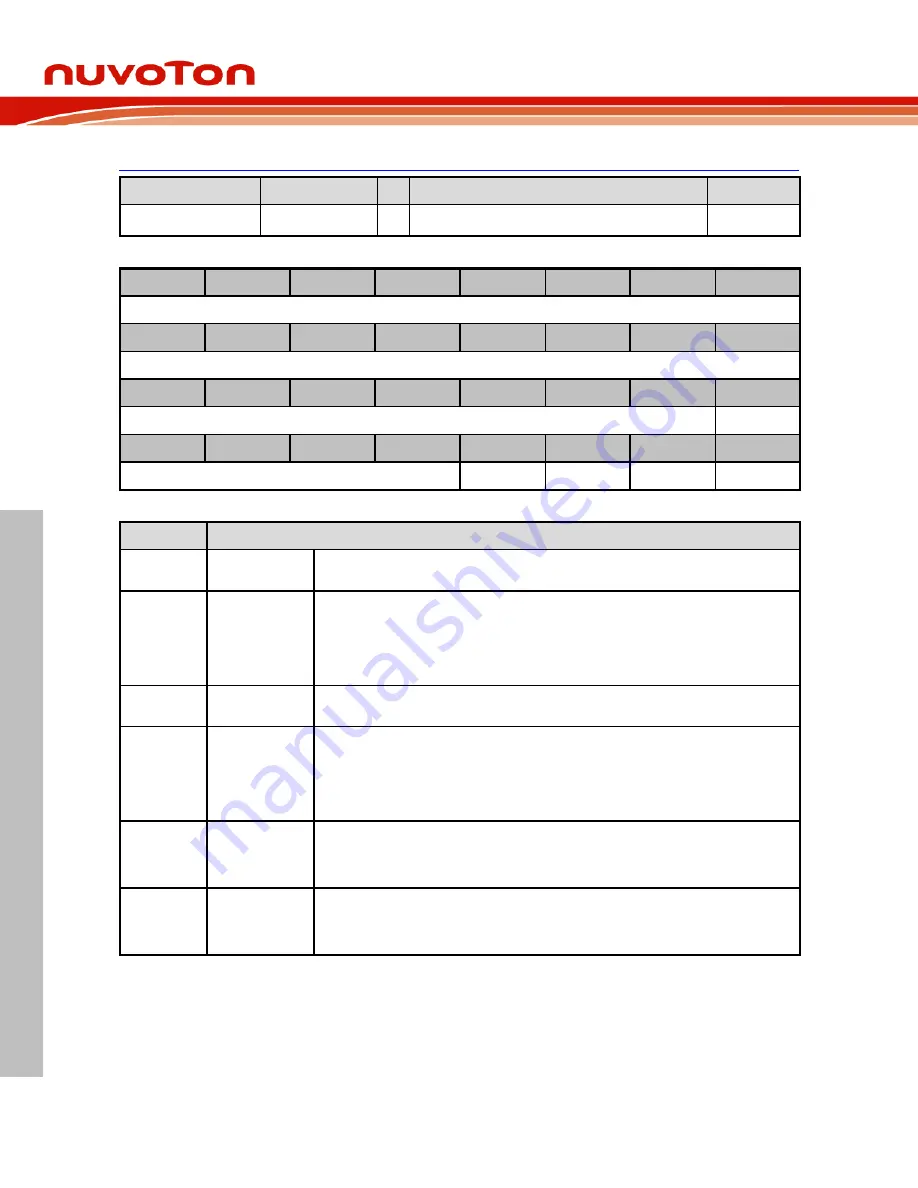

DPWM Status Register (DPWM_STATUS)

Register

Offset

R/W Description

Reset Value

DPWM_STATUS

0x04

R

DPWM Status Register

0x0000_0002

31

30

29

28

27

26

25

24

Reserved

23

22

21

20

19

18

17

16

Reserved

15

14

13

12

11

10

9

8

Reserved

FIFOPTR

7

6

5

4

3

2

1

0

FIFOPTR

Reserved

THIF

EMPTY

FULL

Bits

Description

[31:9]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[8:4]

FIFOPTR

FIFO Pointer (Read Only)

The FULL (DPWM_STATUS[0]) and FIFOPTR (DPWM_STATUS[8:4]) indicates the field

that the valid data count within the DPWM FIFO buffer.

The maximum value shown in FIFOPTR is 31. When the using level of DPWM FIFO buffer

equal to 32, The FULL (DPWM_STATUS[0]) is set to 1.

[3]

Reserved

Reserved. Any values read should be ignored. When writing to this field always write with

reset value.

[2]

THIF

FIFO Threshold Interrupt Status (Read Only)

0 = The valid data count within the FIFO data buffer is more than the setting value of TH

(DPWM_CTL[16:12]).

1 = The valid data count within the FIFO data buffer is less than or equal to the setting value

of TH (DPWM_CTL[16:12]).

[1]

EMPTY

FIFO Empty (Read Only)

0 = FIFO is not empty.

1 = FIFO is empty.

[0]

FULL

FIFO Full (Read Only)

0 = FIFO is not full.

1 = FIFO is full.