ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

197

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

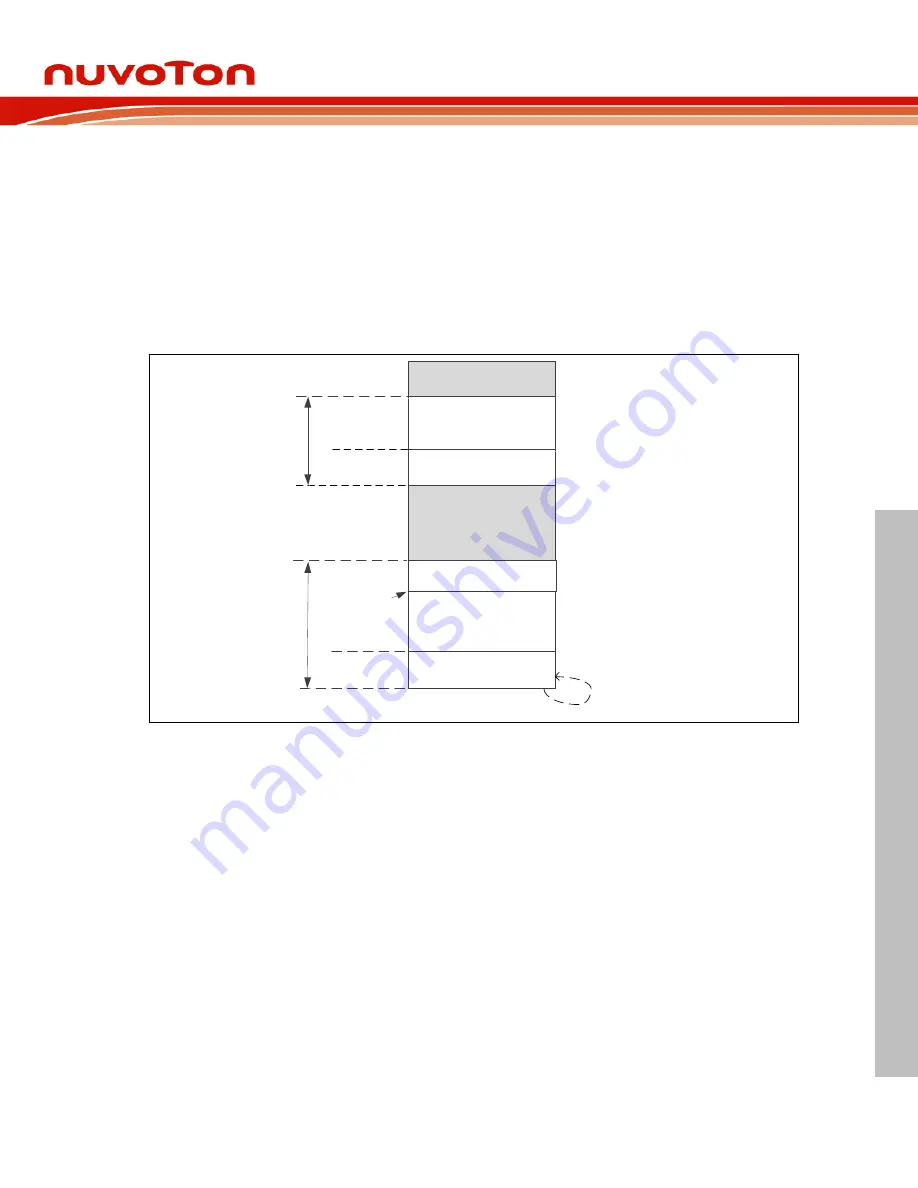

6.4.4.2.2 Boot from APROM with IAP support

By writing 0b10 into CBS[1:0] bits in CONFIG0, the ISD94100 device will load the system vector

table from APROM space 0x0000_0000 - 0x0000_01FF. In this mode, except that the MCU boots

from APROM, all other functions as the same as “boot from LDROM with IAP support” mode.

It has the access to all memory space, can read, erase write any other part of the APROM and

LDROM. It supports IAP and remapping. Remapping can be done by first writing the target remap-

to address to FMC_ISPADDR register and then triggering ISP procedure with the “Vector Remap”

command (0x2E). The targeted remapping address needs to be in alignment with 512bytes.

0x0000_0000

0x0010_0000

0x0010_0FFF

ApplicationROM

(APROM)

Loader ROM

(LDROM 4KB)

Reserved

Reserved

DFBA

0x0000_01FF

0x0000_0200

System Vector Table

512

KB

Data Flash

0x0007_FFFF

0x0010_01FF

4

KB

0x0010_0200

Mapping to

Figure 6.4-5 Boot from APROM with IAP support

6.4.4.2.3 Boot from LDROM without IAP support

By writing 0b01 into CBS[1:0] bits in CONFIG0, the ISD94100 device will load the system vector

table from LDROM space 0x0010_0000 - 0x0010_01FF. In this mode the MCU boots from LDROM,

and only has the access to LDROM, as shown in Figure 6.4-6.