ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

834

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

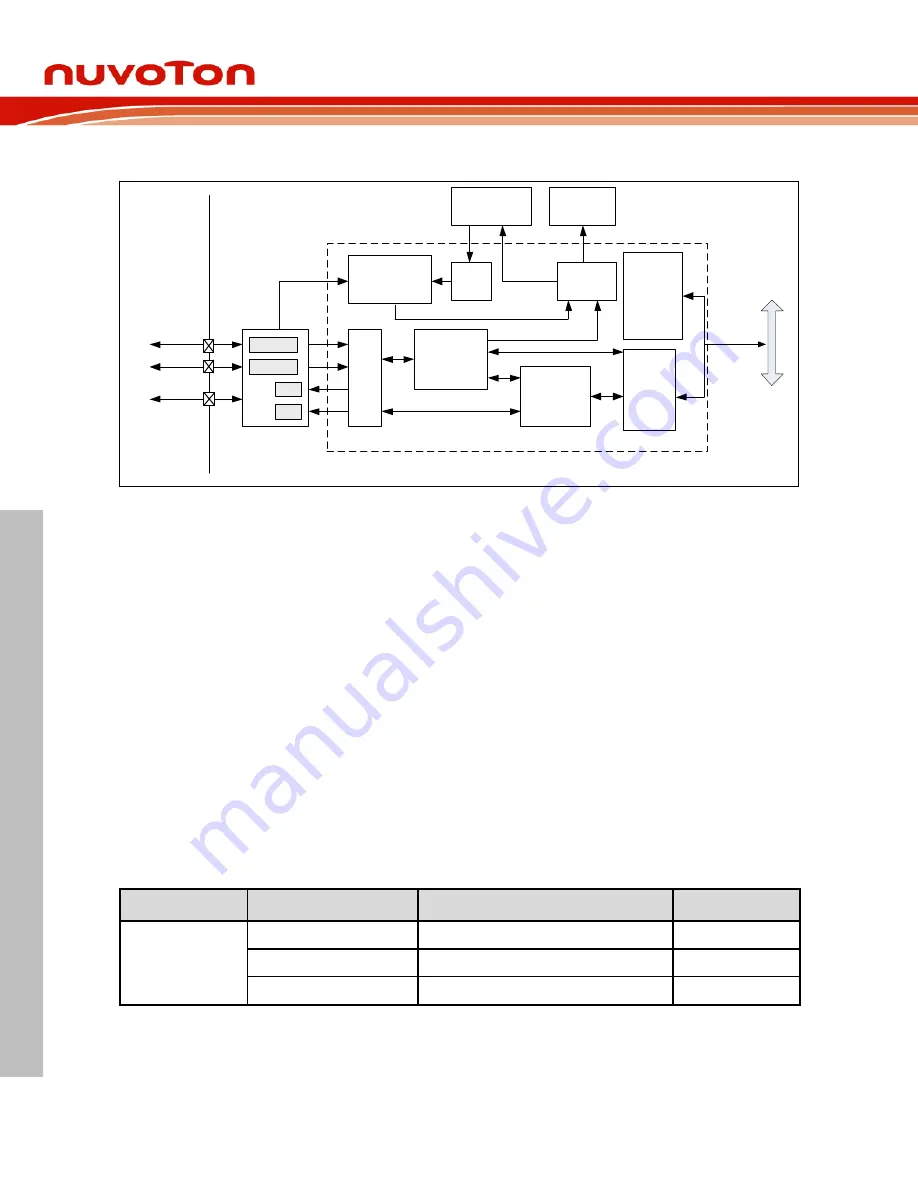

6.18.3 Block Diagram

RXDP

RXDM

S0

S1

Transceiver

USB_D+

USB_D-

SIE

VBUS

Detection

De-bouncing

DPLL

Endpoint

Control

Buffer

Control

SRAM

(1K

Bytes)

APB Bus

USB

control

and

status

registers

Interrupt

control

Clock

Generator

NVIC

VBUS

Detection

USB_VBUS

Figure 6.18-1 USB Block Diagram

6.18.4 Basic Configuration

The role of USB frame is determined by USBROLE (SYS_USBPHY[1:0]). The internal USB 3.3V

LDO can be enabled by LDO33EN (SYS_USBPHY[8]). These two configurations are write-

protection bits. Before writing to these bits, user must disable the register protection function. Refer

to the description of SYS_REGLCTL register for details. The USBD clock source is derived from

PLL. User has to set the PLL related configurations before USB device controller is enabled. Set

the USBDCKEN (CLK_APBCLK0[27]) bit to enable USBD clock and 4-bit pre-scaler USBDIV

(CLK_CLKDIV0[7:4]) to generate the proper USBD clock rate.

Clock source configuration

–

Setting PLL controller (CLK_PLLCTL).

–

Select the clock divider number of USBD peripheral clock on USBDIV

(CLK_CLKDIV0[7:4]).

–

Enable USBD peripheral clock in USBDCKEN (CLK_APBCLK0[27]).

Reset configuration

–

Reset USBD controller in USBDRST (SYS_IPRST1[27]).

Pin configuration

Group

Pin Name

GPIO

MFP

USB

USB_D+

PB.13

MFP1

USB_D-

PB.14

MFP1

USB_VBUS

PB.15

MFP1

Note:

If GPIO configure as USB function, the register PB_MODE[31:26] should be set to 0 and

PUSEL15 (PB_PUSEL[31:30]) should be set to 2.